## Connections to the Beginning: Circuit Boards for CERN

Dillon Acker-James, Electrical Computing Engineering Major

Mentor: Aditya Dalakoti

Faculty Advisor: Professor Forrest Brewer, Electrical

**Computer Engineering**

Funding: High Granularity Calorimeter Studies (HGCAL)

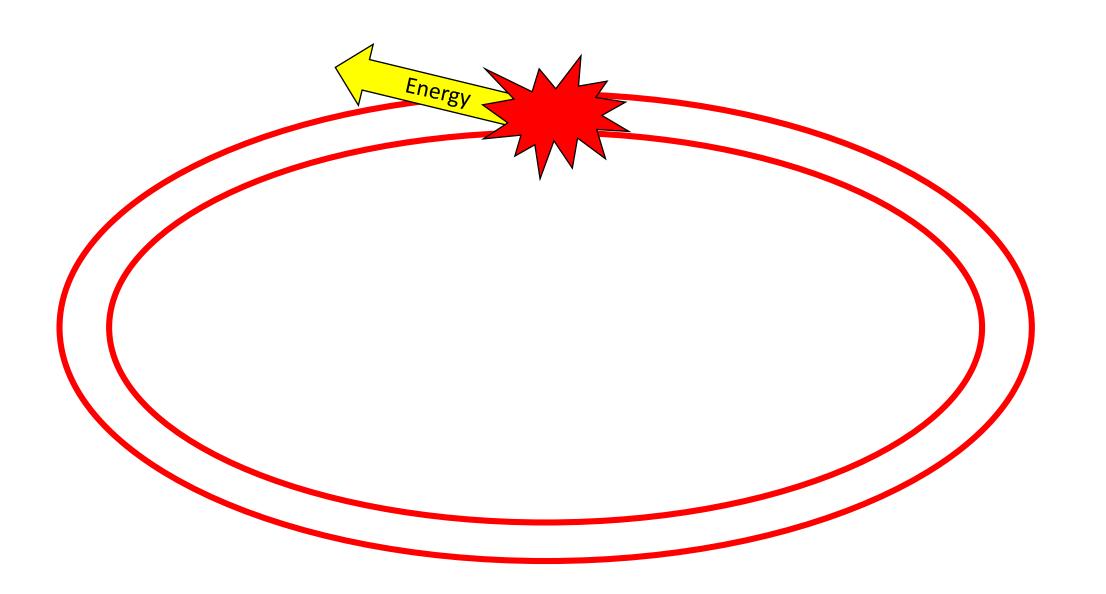

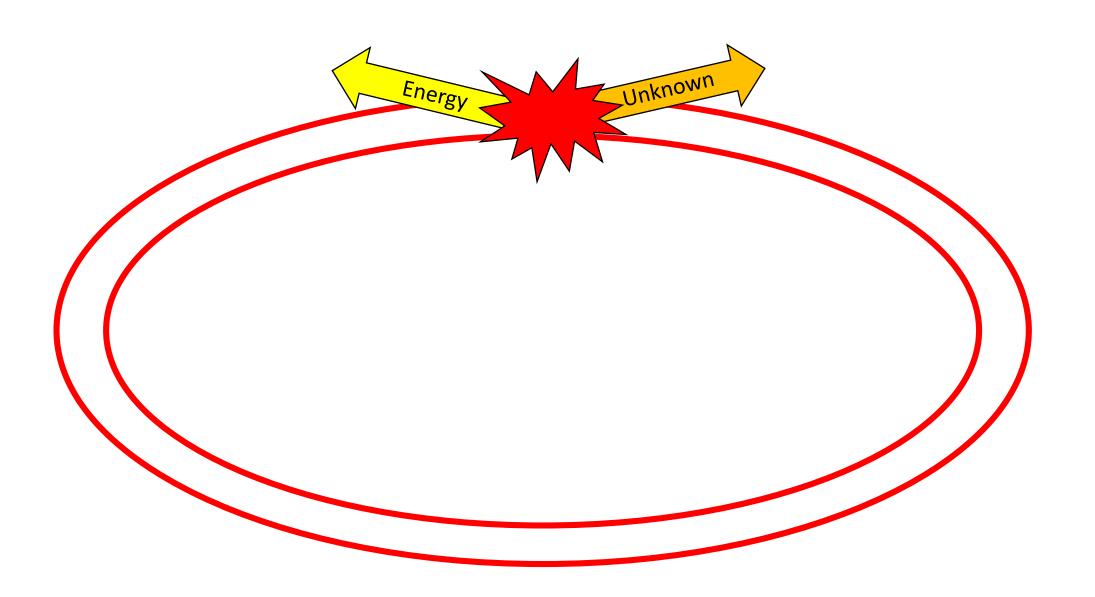

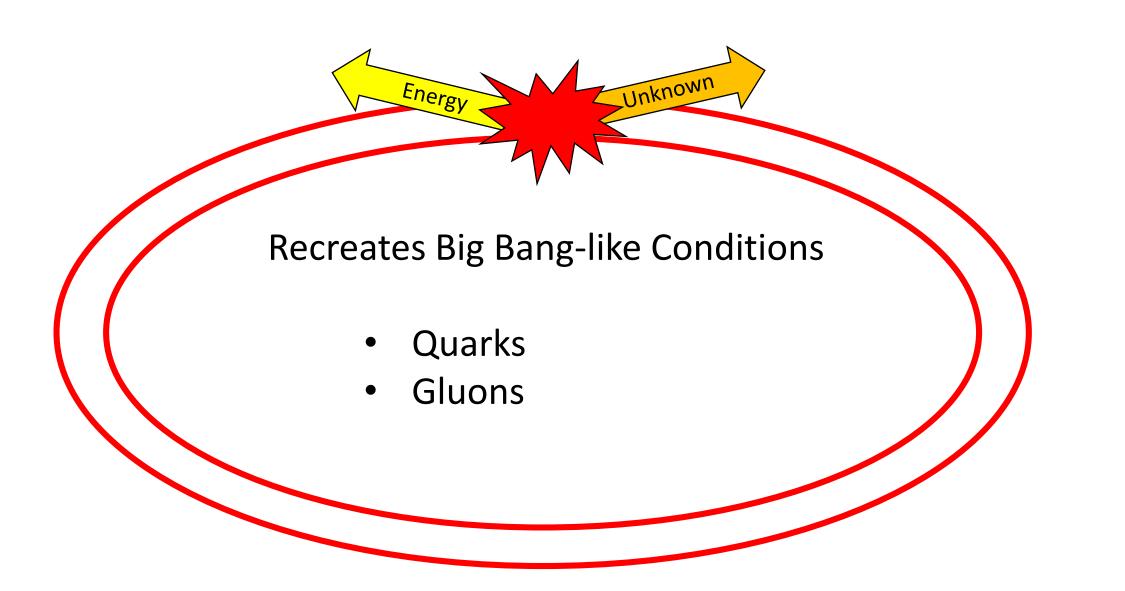

15 Million Kelvin

15 Million Kelvin

5.5 Trillion Kelvin

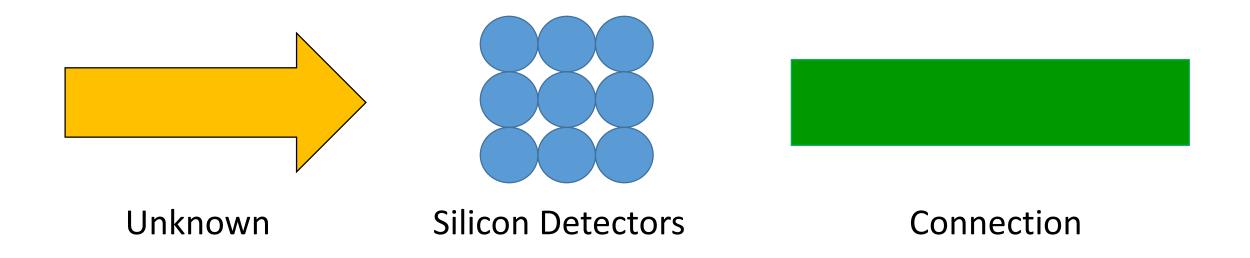

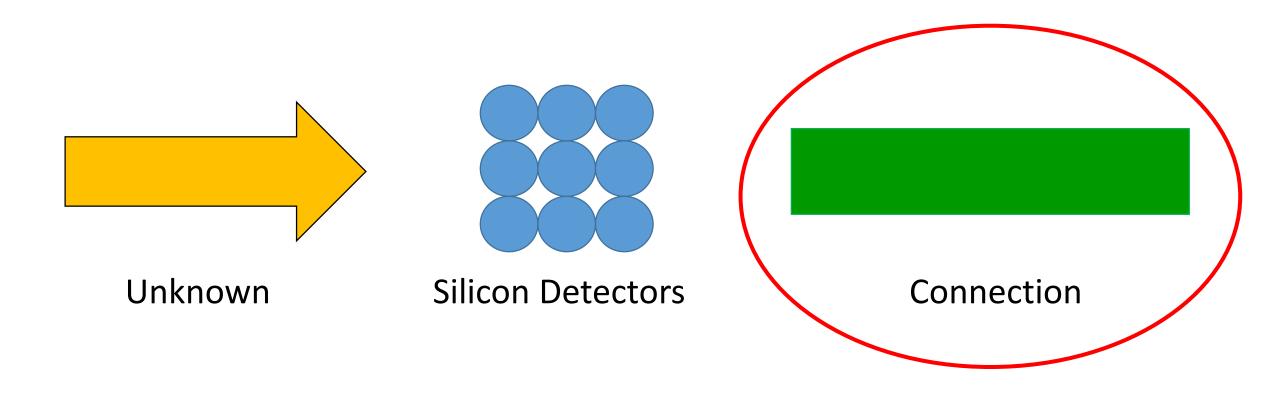

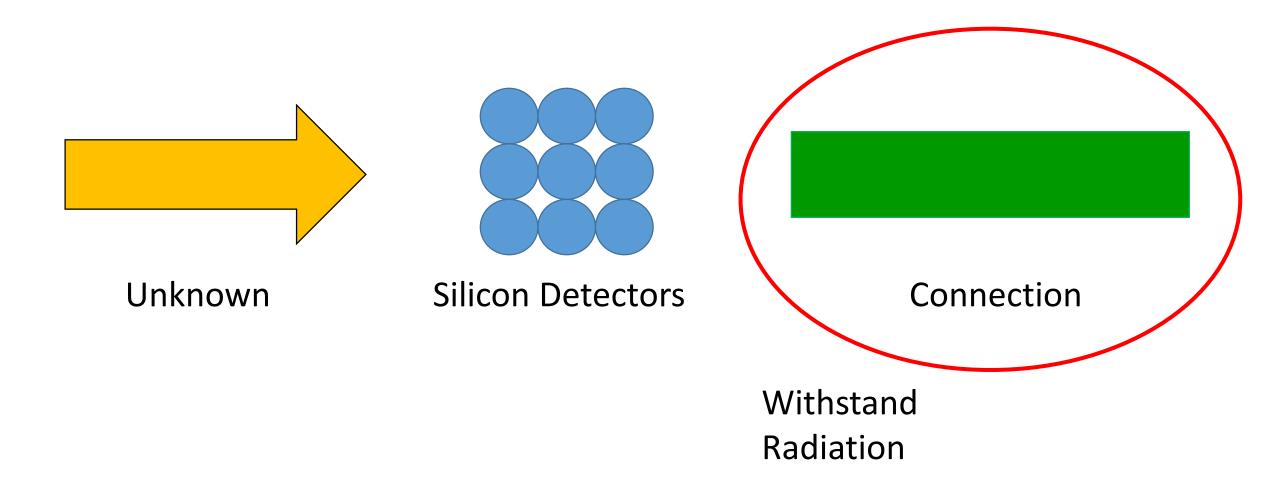

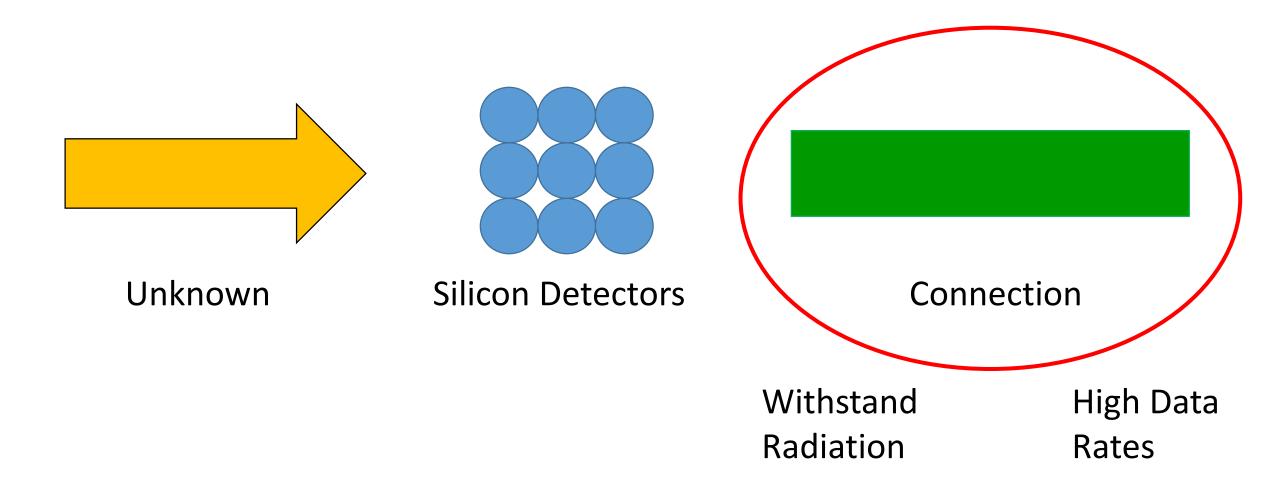

Unknown

Space

Power

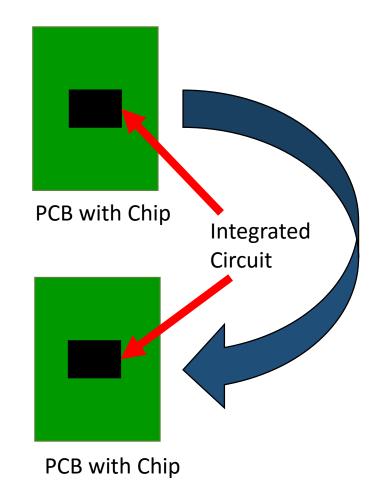

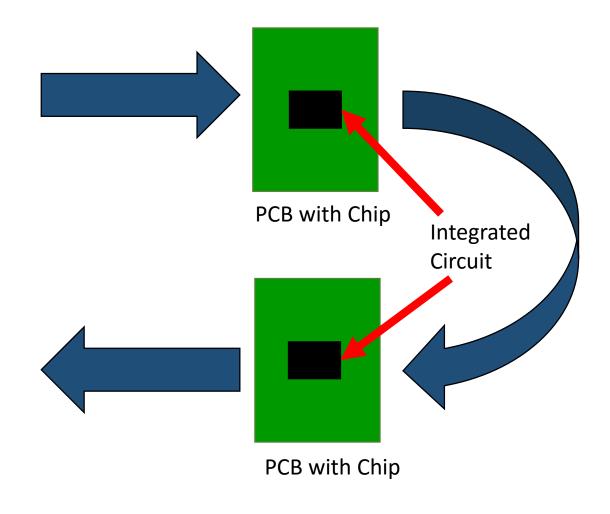

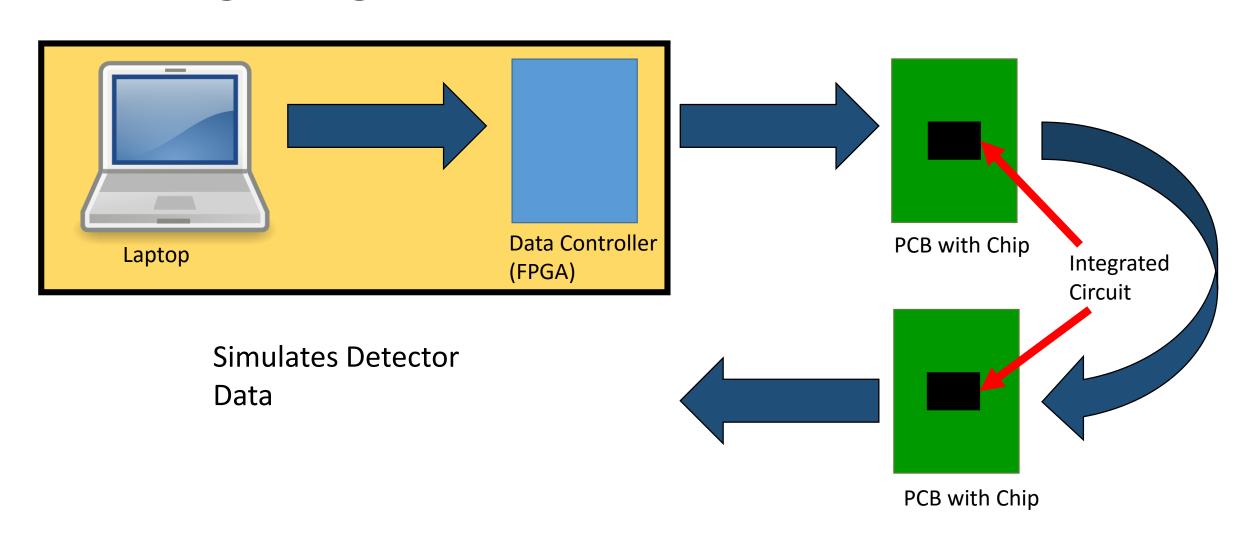

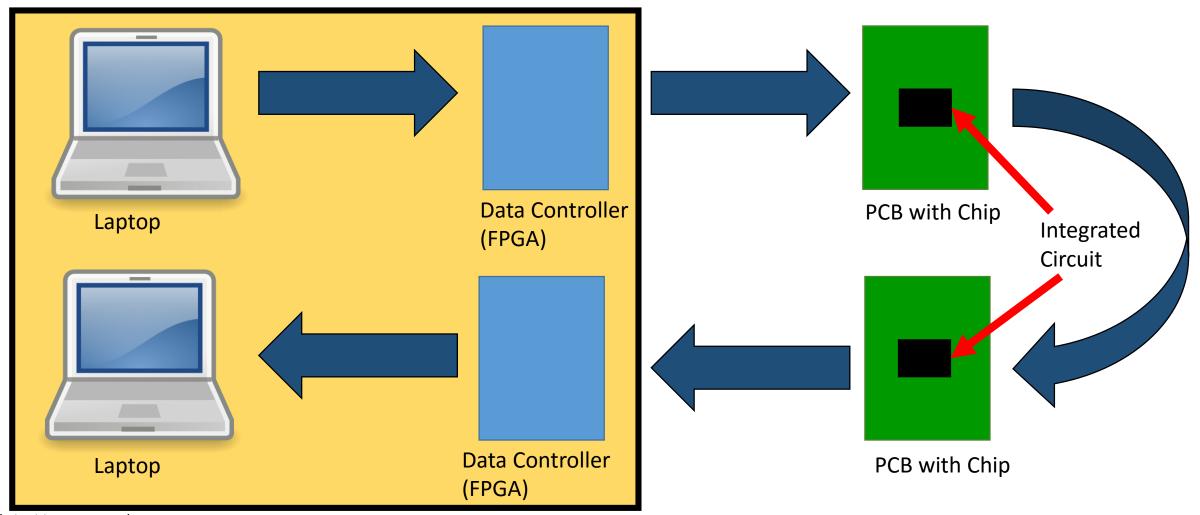

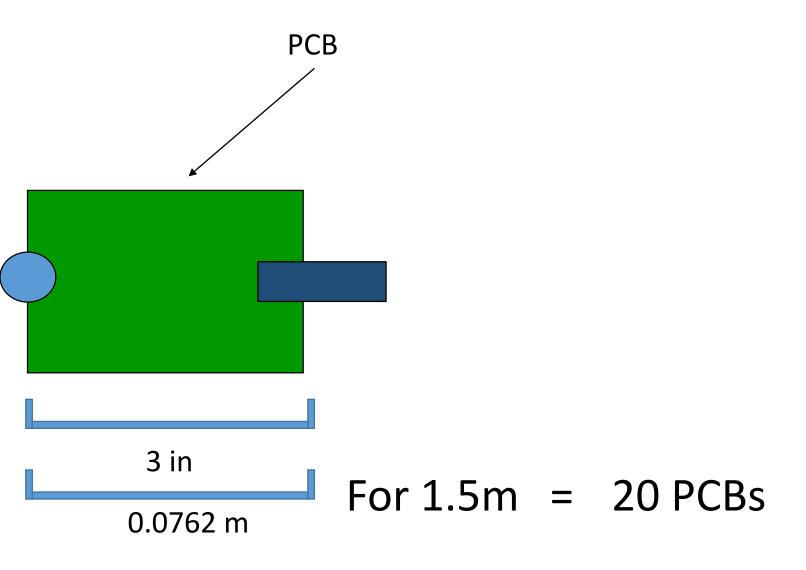

#### **Test Integrated Circuits**

**Test Integrated Circuits**

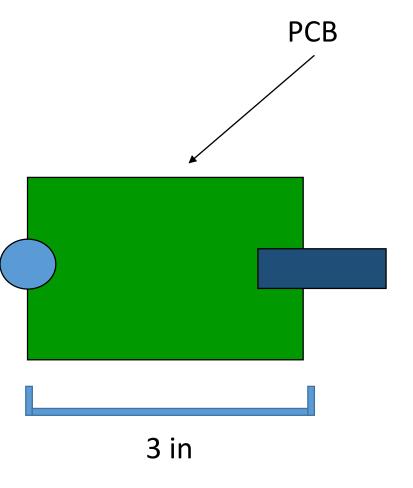

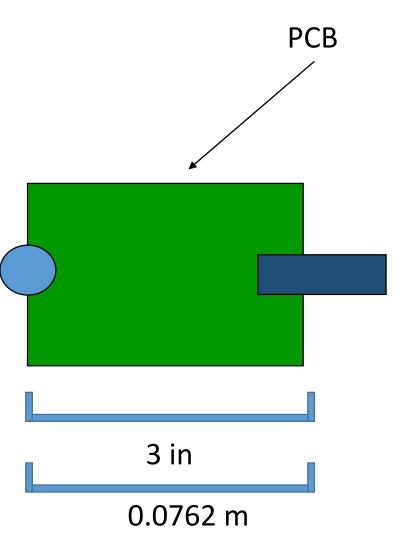

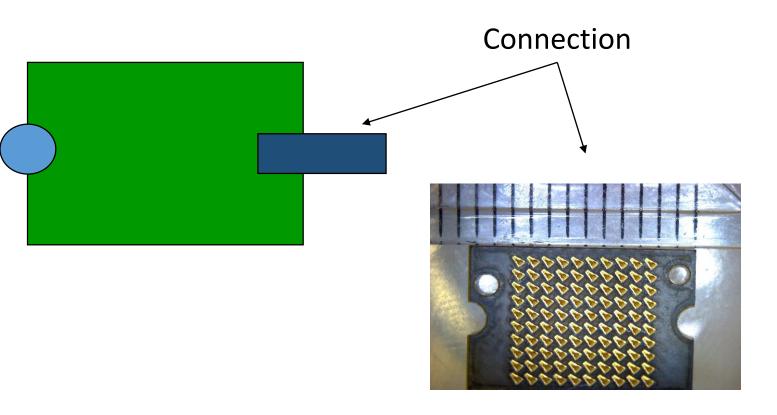

Make a Long PCB

**Test Integrated Circuits**

Make a Long PCB

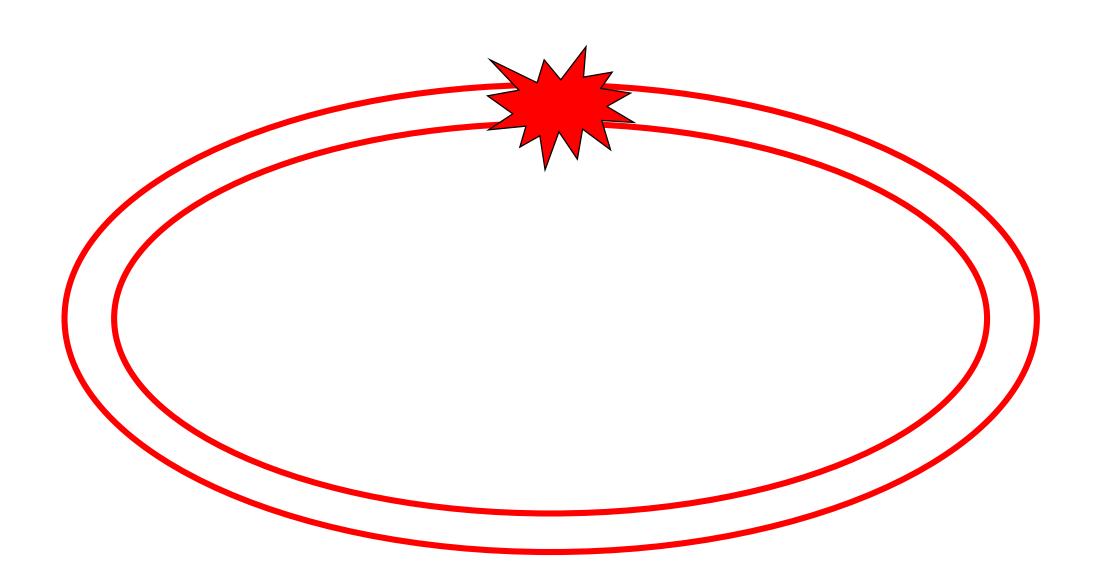

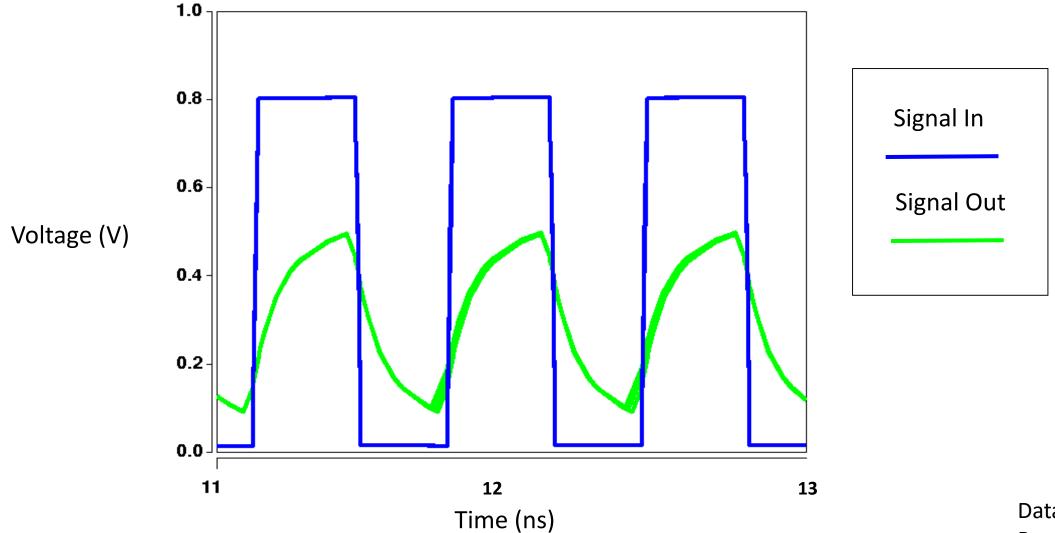

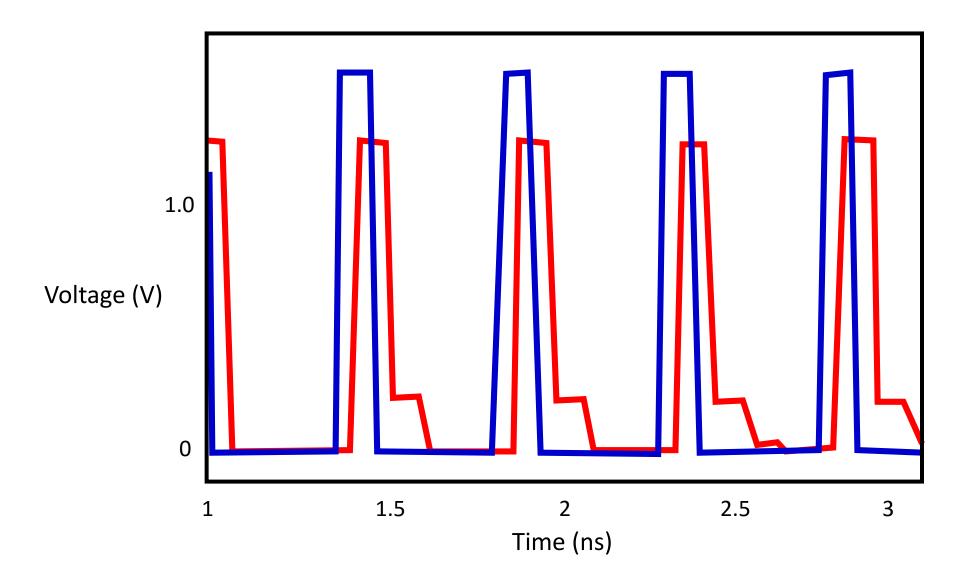

## Transmission Causes Loss of Data and Imperfections Cause Reflection

#### Transmission Causes Loss of Data

Data from Prof. Brewer's Lab

## Transmission Causes Loss of Data and Imperfections Cause Reflection

## Imperfections Cause Reflection

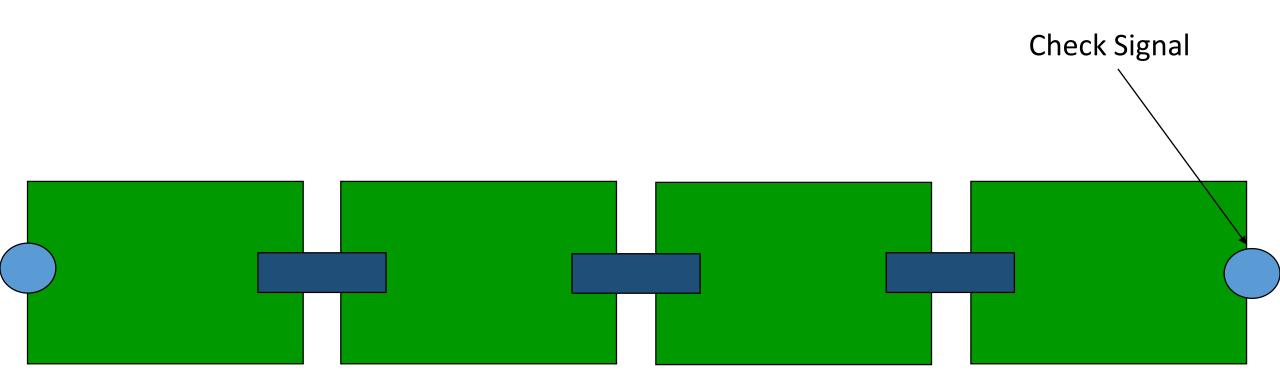

Signal In

Signal Out

Data from Prof. Brewer's Lab

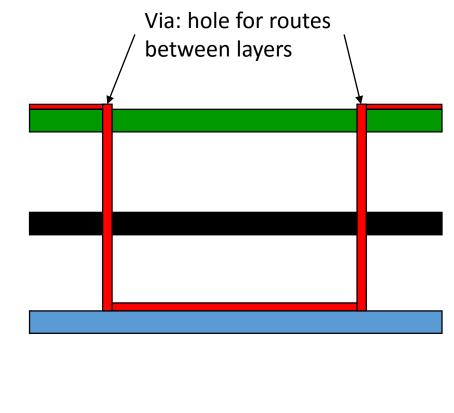

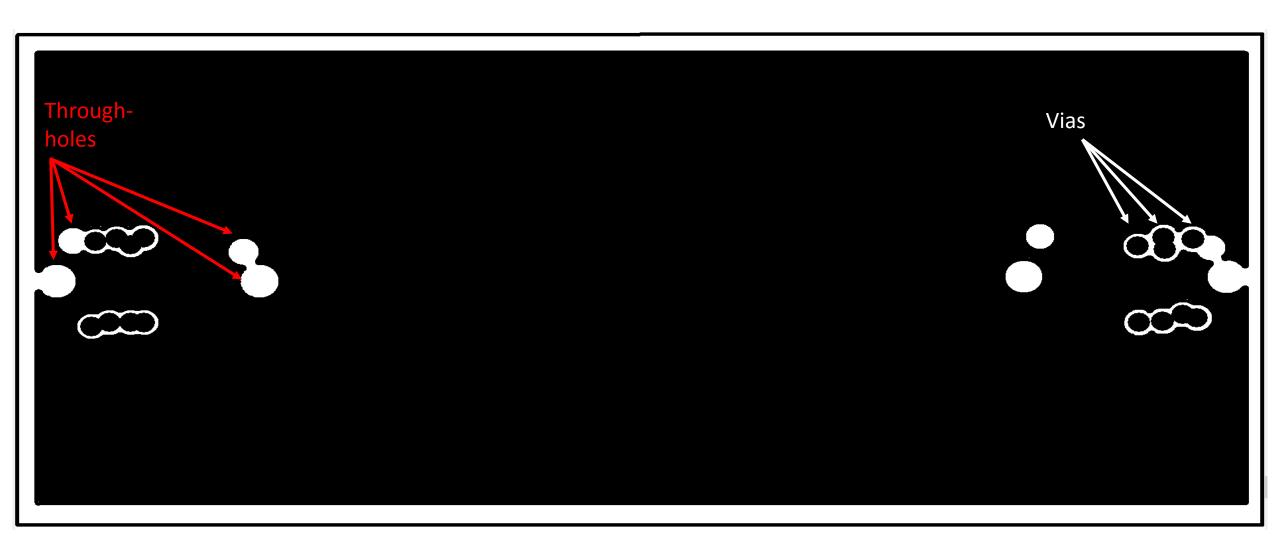

Ground Layer

Signal Layer

Ground Layer

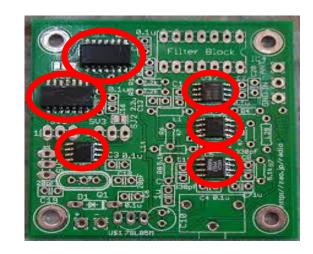

## Component Layer

## Component Layer

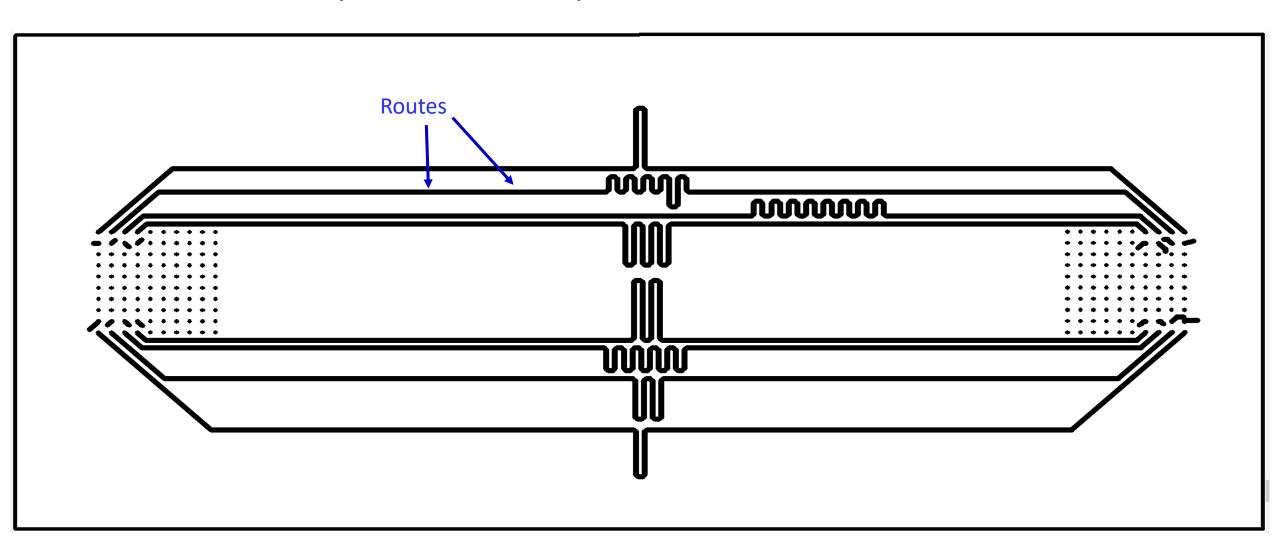

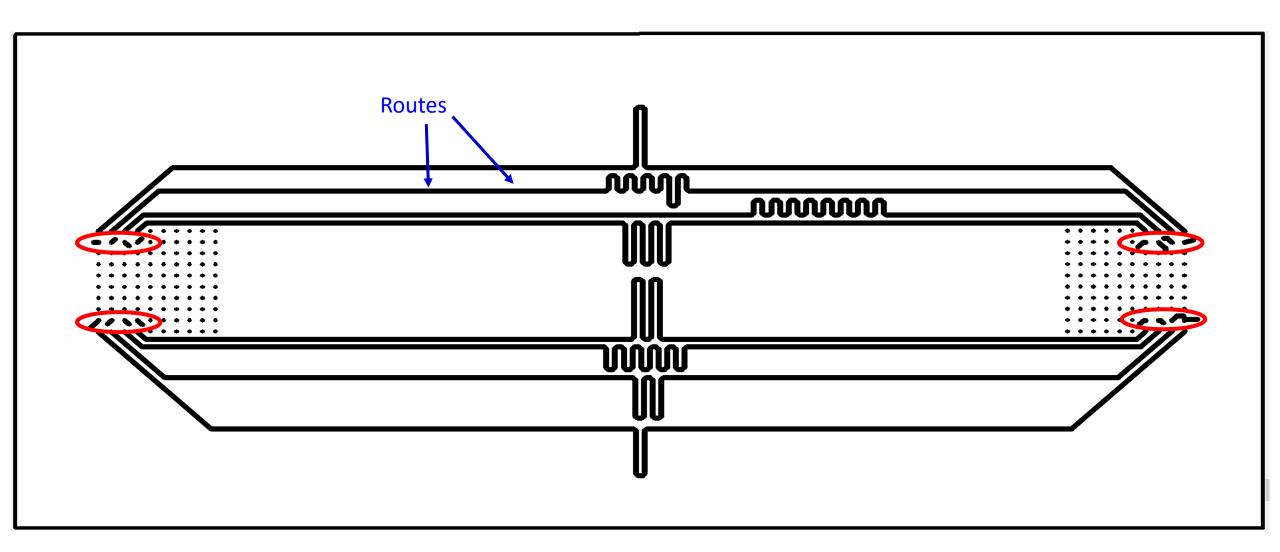

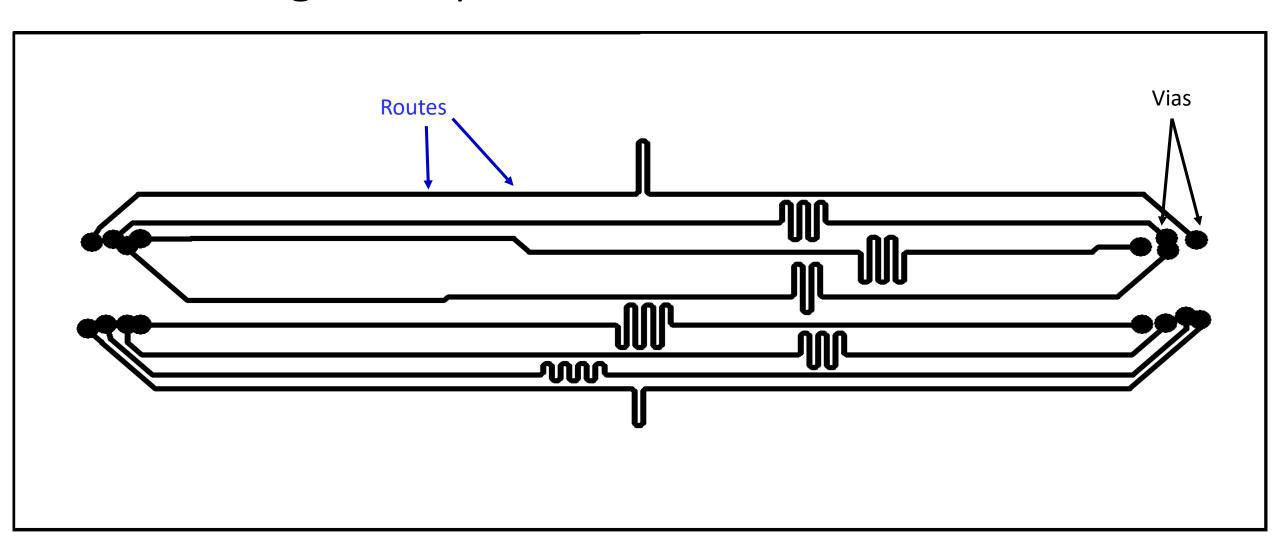

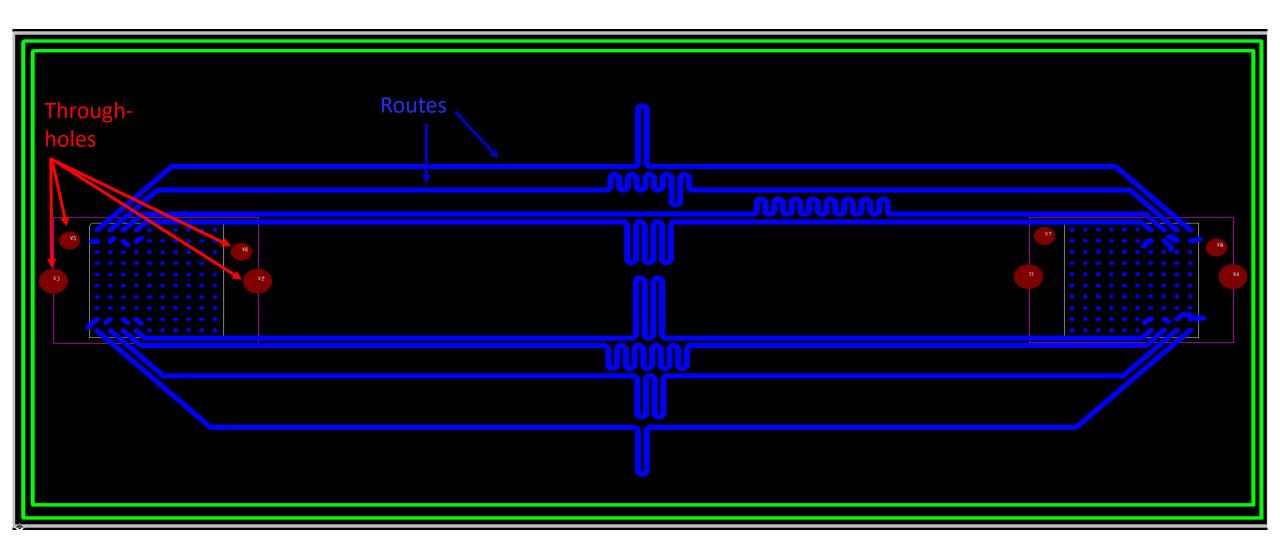

Route: copper connection Component Layer Ground Layer Signal Layer Ground Layer

Component Layer

Ground Layer

Signal Layer

**Ground Layer**

Through-hole: hole through entire board for screws Component Layer Ground Layer Signal Layer Ground Layer

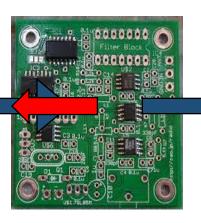

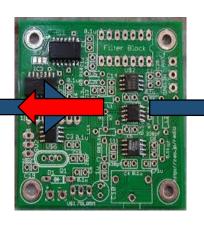

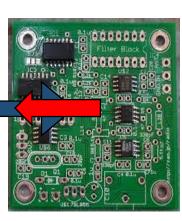

### Unrouted Board

## First: Component Layer

## First: Component Layer

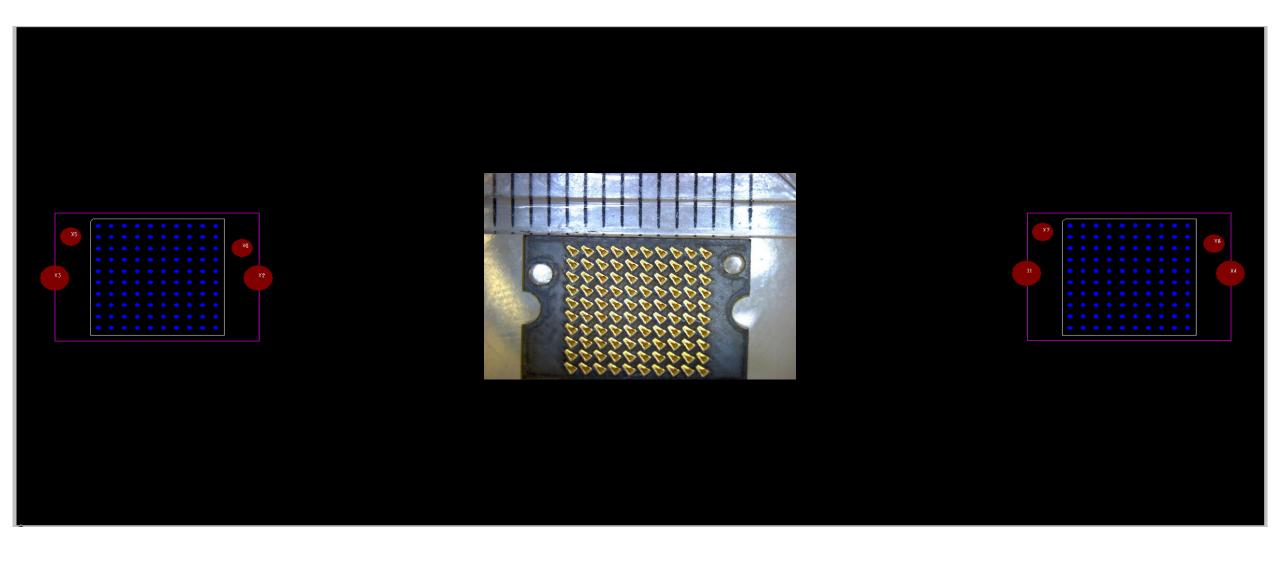

## Second: Ground Layer

## Third: Signal Layer

# Fourth: Bottom Layer

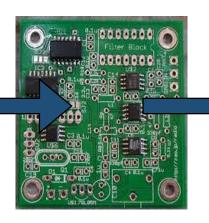

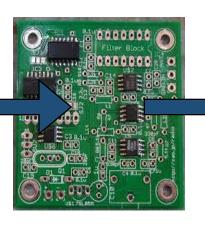

#### Finished Board

http://3.bp.blogspot.com/-DeP9JcQKO2j7ez0/s1600/computer%2Bemoji.png

#### Acknowledgements

**Professor Forrest Brewer**

The Brewer Lab

**EUREKA** and **CSEP**

Aditya Dalakoti

#### PCBs Vs. Wires

1,000 PCBS

#### PCBs Vs. Wires

1,000 PCBS

100,000 Wires